? ? 隨著科學技術的發展,日益廣泛采用的微電子技術和電氣化的逐步實現,形成了復雜的電磁環境。有些產品在雷雨季節時運行,經常會有大量部件損壞;還有一些產品,在實驗調試階段,每一樣指標、性能都完美適配,但到了客戶手里卻小毛病不斷。

? ? 這些問題當中,有相當一部分都源于電磁干擾。所以,不斷研究和解決電磁環境中設備之間以及系統間相互關系的問題,促進了電磁兼容技術的迅速發展。

電磁干擾

? ? 電磁兼容(EMC)是設備或系統在其電磁環境中能正常工作且不對該環境中任何事物構成不能承受的電磁干擾的能力。

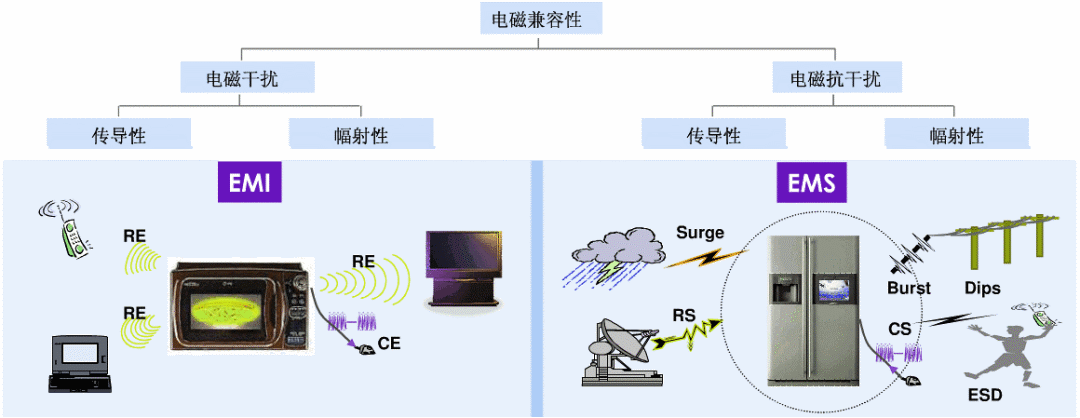

? ? EMC由兩部分構成:電磁干擾(EMI)和電磁抗擾度(EMS),電磁干擾是指設備或系統對外發射的干擾,不能超過限值;而電磁抗擾度是指設備或系統能夠抵抗外界環境電磁干擾的最小值。

? ? 電磁干擾形成的三要素分別為干擾源,傳播途徑以及敏感設備。一般情況下EMI整改往往是從干擾源以及傳播路徑上入手的,即抑制干擾源和切斷傳播路徑。

EMI抑制方案

? ? 以音頻產品為例,抑制傳導EMI措施主要可分為抑制干擾源以及傳播路徑的優化兩大方向。

01.抑制干擾源方向

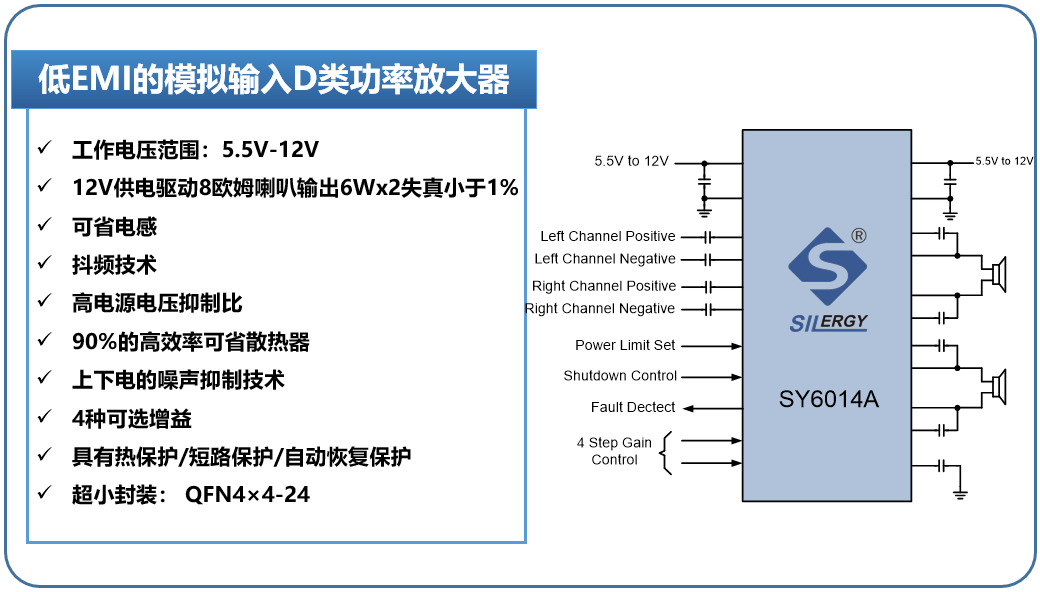

D類功放產品存在功率管高頻開關動作,這樣勢必會造成較差的傳導EMI進而影響系統中其他電路,矽力杰現有產品中有如下優化措施:

1. 抖頻技術:

將原來單一的開關頻率擴展到一定的范圍內,從而降低頻譜中單個尖峰的高度。

SY6014/SY6014A是高性能模擬D類功放芯片,采用偽隨機頻率抖動技術,將原本的單一峰值能量擴展為一個頻帶的平均能量,使得該頻帶內的峰值能量下降6dB。

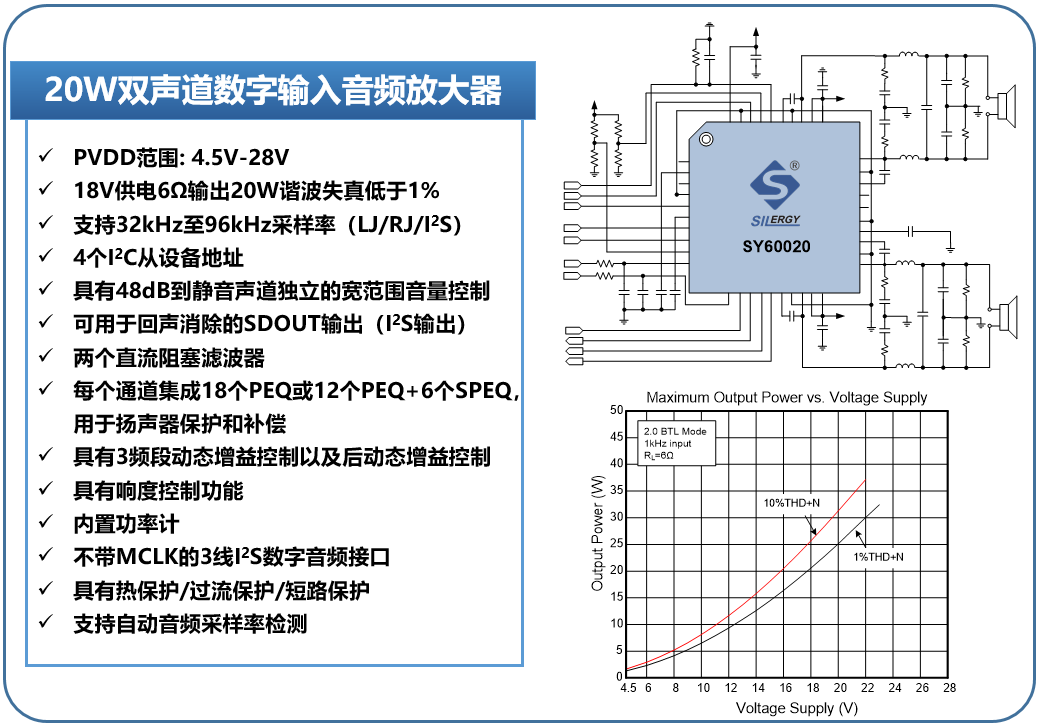

2. 相位延遲技術:

針對多通道輸出的產品,將各路的PWM輸出之間增加相位延遲,進而減小頻譜上對應頻率的峰值。

SY6045B/SY60020是I2S輸入集成高性能DSP支持雙通道的數字輸入音頻放大器, 其每一路的驅動部分均可以通過I2C設置相位延遲, 在電視應用中,通過調節相位延遲, 使其在不影響音頻性能的前提下,EMI傳導干擾降低5.5dB。

3. 邊沿控制技術:

優化驅動電路,有效控制開關上升下降沿,減少輸出邊沿的振鈴。矽力杰模擬/數字音頻功放芯片中皆進行了功率管驅動電路的優化。

4. 增加緩沖電路:

在PWM輸出節點增加合適的緩沖電路,可以改善邊沿時間,從而改善EMI。

02.傳播路徑的優化

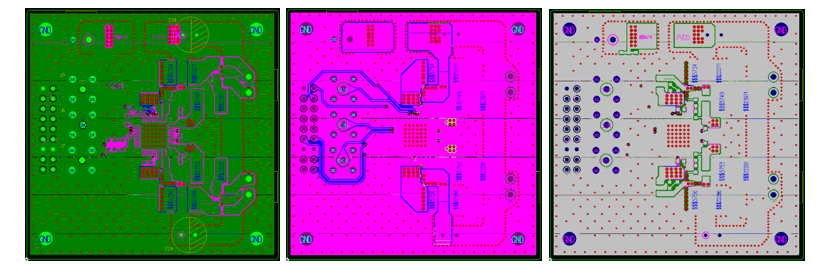

傳播路徑的優化主要可通過優化PCB布局布線來提高抗電磁干擾性能。

1. 地平面屏蔽:

盡量將功率走線和信號走線置于中間層,用頂層和底層整片的地平面包圍。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 頂層:接地? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?中間層:信號/電源? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?底層:接地

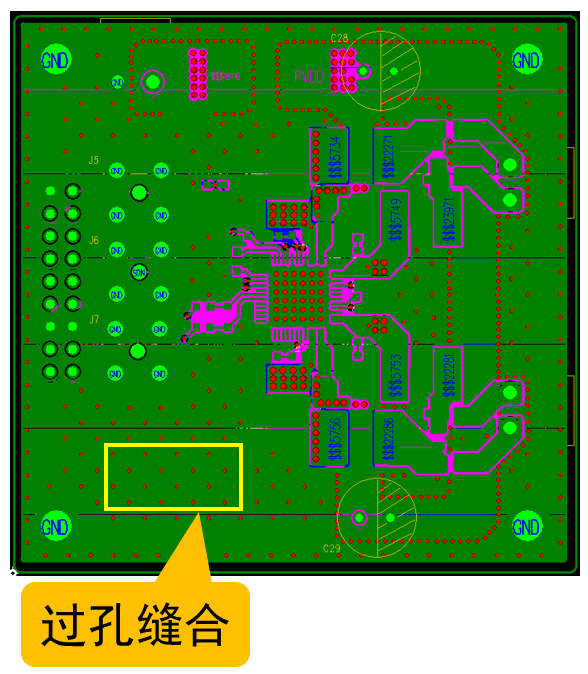

2. 過孔縫合:

將所有的地平面使用大量等間距的過孔連接起來。

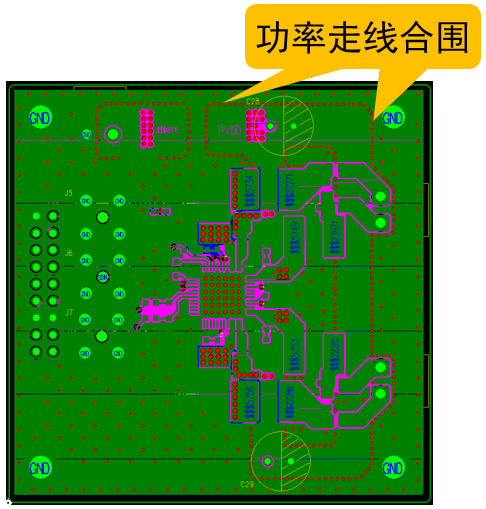

3.?功率走線合圍:

同樣用過孔沿功率走線均勻布置以提供最近的低阻抗路徑

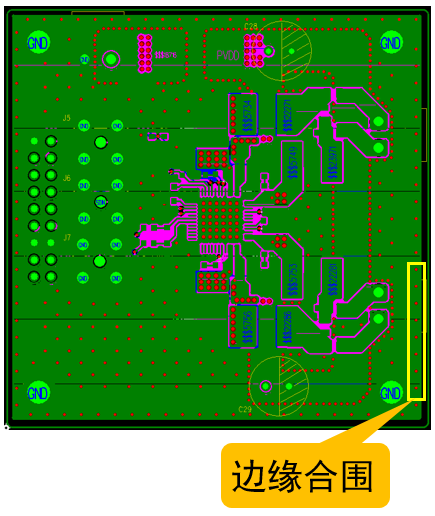

4. 邊緣合圍:

將PCB板邊緣同樣用過孔合圍,可以減小板邊緣的電容效應從而改善EMI。

? ? 在音頻領域中,電磁干擾不僅會影響產品的工作可靠性,還經常會耦合到音頻信號的路徑中。低EMI電路設計可以避免不必要的PCB重新制造,節省開發成本和時間,確保電子產品按時甚至提前進入消費者視野。